## 전자회로

문 1. 다음 회로에 대한 설명으로 옳지 않은 것은?

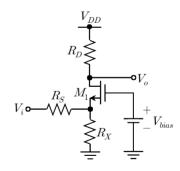

- ① 회로를 증폭기로 사용하기 위해서는 트랜지스터  $M_1$ 이 포화 영역(saturation region)에서 동작하도록 DC 동작조건을 설정해야 하다.

- ② 회로가 증폭기로 동작하고 다른 모든 조건이 동일할 때 전압 이득  $|A_v|$ 은 저항  $R_s$ 의 크기가 클수록 커진다.

- ③ 회로가 증폭기로 동작하고 다른 모든 조건이 동일할 때 전압 이득  $|A_v|$ 은 저항  $R_D$ 의 크기가 클수록 커진다.

- ④ 트랜지스터  $M_1$ 에 게이트 누설전류(gate leakage current)가 없을 때 입력에서 바라본 입력저항은 무한대의 값을 갖는다.

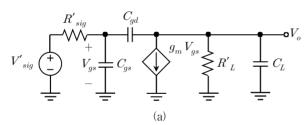

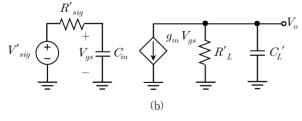

- 문 2. 밀러(Miller) 정리를 이용하여 그림 (a)의 회로를 그림 (b)의 등가회로로 바꾸었을 때  $C_{in}$ 과  $C_{L}^{'}$ 의 표현식으로 올바른 것은?

(단,

$$K$$

는  $\frac{V_o}{V_{gs}}$ 이다)

$$C_{in}$$

$$C_{L}^{'}$$

①

$$C_{gs} + C_{gd}(1 - K)$$

$$\begin{array}{ccc} \underline{C_{in}} & \underline{C_L^{'}} \\ & & \underline{C_L^{'}} \end{array}$$

$$(1) \quad C_{gs} + C_{gd}(1-K) & C_L + C_{gd} \left(1-\frac{1}{K}\right) \end{array}$$

$$C_L + C_{gd}(1 - K)$$

(3)

$$C_{gs} + \frac{C_{gd}}{(1-K)}$$

$C_L + \left(\frac{C_{gd}}{1-\frac{1}{K}}\right)$

$$C_L + \left(\frac{C_{gd}}{1 - \frac{1}{K}}\right)$$

$$\textcircled{4} \quad C_{gs} + \left(\frac{C_{gd}}{1 - \frac{1}{K}}\right) \qquad \qquad C_L + \frac{C_{gd}}{(1 - K)}$$

$$C_L + \frac{C_{gd}}{(1 - K)}$$

- 문 3. 10 [kHz]의 신호파와 100 [MHz]의 반송파를 가지고 최대 주파수 편이를 50 [kHz]로 하여 주파수 변조(FM)를 하였을 때, 대역폭 BW[kHz]는?

- ① 20

- ② 100

- 3 120

- 4) 150

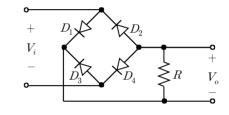

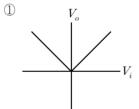

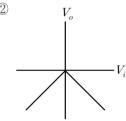

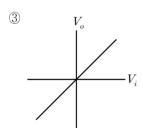

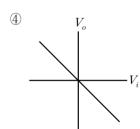

- 문 4. 다음 회로에서 입력전압( $V_i$ )과 출력전압( $V_i$ )의 관계를 옳게 표시한 것은? (단, 네 개의 다이오드는 모두 이상적이라고 가정 하다)

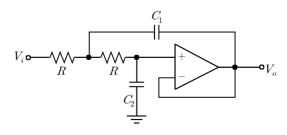

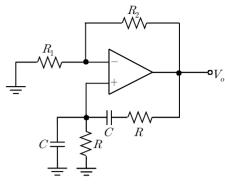

문 5. 다음 회로의 전달함수는  $H(s) = \frac{V_O(s)}{V_I(s)} = \frac{1}{1 + sX + s^2(R^2C_1C_2)}$

이다. X에 적합한 것은? (단, 연산증폭기는 이상적이라고 가정한다)

- ①  $RC_1$

- $2RC_1$

- $3 RC_2$

- 4  $2RC_2$

문 6. 다음 쌍안정 회로에서 높은 쪽 문턱전압  $V_{TH}[{

m V}]$ 와 낮은 쪽 문턱전압  $V_{TL}[{

m V}]$ 의 값은? (단, 포화전압은  $V_{H}\!=\!\!-V_{L}\!=\!12[{

m V}]$ 이다)

$V_{TH}$   $V_{TL}$  0 0 0

② 24 -24

③ 4 -4

4 8 -8

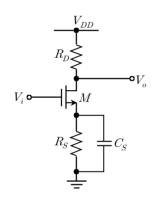

문 7. 다음 회로의 전달함수  $\frac{V_o(s)}{V_i(s)}$  에서 극점(pole)을 올바르게 구한 것은? (단,  $g_m$ 은 M의 전달컨덕턴스이며, 채널길이변조(channel length modulation), 몸체효과(body effect), 기생커패시턴스 성분은 무시한다)

$\bigcirc -\frac{g_m}{C_S}$

$\textcircled{4} \ -\frac{1+g_mR_S}{R_SC_S}$

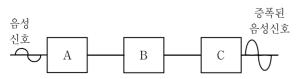

문 8. 다음은 상보형 MOSFET를 이용한 D급 증폭기의 블록다이어그램 이다. A-B-C에 들어갈 명칭을 순서대로 바르게 나열한 것은?

- ① PWM변조기 보상 푸시풀 스위칭 증폭기 저역통과필터

- ② PWM변조기 저역통과필터 보상 푸시풀 스위칭 증폭기

- ③ PCM변조기 보상 푸시풀 스위칭 증폭기 저역통과필터

- ④ PCM변조기 저역통과필터 보상 푸시풀 스위칭 증폭기

문 9. 다음 회로에서  $\frac{R_2}{R_1}$  값을 R과 C의 함수로 바르게 나타낸 것은? (단, 연산증폭기는 이상적이라고 가정한다)

②  $\frac{R_2}{R_1} = \frac{1}{sCR} + 2 + sCR$

$4 \frac{R_2}{R_1} = 2 + s \, CR + s^2 CR$

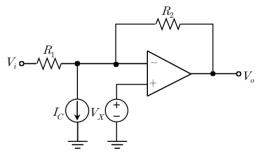

문 10. 다음 회로에서 출력전압  $V_o = -\frac{R_2}{R_1}\,V_i$ 가 되기 위한  $I_C$ 와  $V_X$ 의 조건은? (단, 연산증폭기는 이상적이라고 가정한다)

①  $I_C = -\frac{1}{R_1} V_X$

$② I_C = -\frac{1}{R_2} V_X$

$(3) I_C = -\left(\frac{1}{R_1} + \frac{1}{R_2}\right) V_X$

$\textcircled{4} \ \ I_{C} \! = \! - \! \left( \! 1 \! + \! \frac{R_{2}}{R_{1}} \right) \! \frac{1}{R_{1}} \, V_{X}$

문 11. 다음 카르노 맵(Karnaugh map)에 대한 논리식으로 옳은 것은?

| x | yz 00 | 01 | 11 | 10 |

|---|-------|----|----|----|

| 0 | 1     | 1  |    | 1  |

| 1 | 1     | 1  | 1  | 1  |

②  $F = x + \bar{y} + z$

(3)  $F = x + \bar{y} + \bar{z}$

$4 F = \bar{x} + y + z$

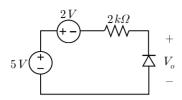

문 12. 다음 회로에서 출력전압  $V_o[V]$ 는? (단, 다이오드는 이상적이라고 가정한다)

- ① 1.5

- ② 2

- ③ 3

- **4**) 5

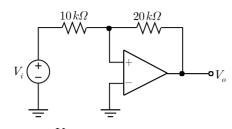

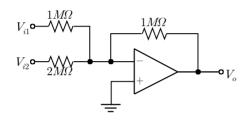

- 문 13. 다음 회로에서  $V_{i1} = 1$  [V],  $V_{i2} = 2$  [V]일 때 출력전압  $V_o$  [V]는? (단, 연산증폭기는 이상적이라고 가정한다)

- ① 2

- (2) -2

- ③ 5

- (4) -5

- 문 14. 출력 구조가 개방 드레인(open-drain)인 논리게이트(logic gate)에 대한 설명으로 옳지 않은 것은?

- ① 정상적인 출력전압을 얻기 위해서는 드레인 단자를 풀업저항 (pull-up resistor)을 통해 전원에 연결해야 한다.

- ② 개방 드레인 출력 단자들끼리 결선-AND(wired-AND) 연결이

- ③ 서로 다른 전원전압을 사용하는 논리게이트와의 인터페이스에 사용할 수 있다.

- ④ 일반적으로 표준 CMOS 논리게이트에 비해 출력단의 회로가 복잡하다.

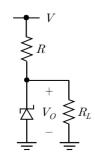

- 문 15. 다음 회로에서 5[V] 제너다이오드가 동작하기 위해서는 최소 전류 1 [mA]가 다이오드에 흘러야 한다.  $V=11[V], R=1[\text{k}\Omega]$ 인 경우  $V_o=5$  [V]를 유지할 수 있는 저항  $R_L[\mathbf{k}\Omega]$ 의 최솟값은?

- ① 1

- 2 5

- 3 6

- 4 11

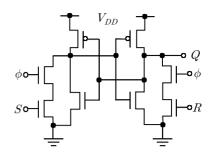

문 16. 다음 회로에 대한 진리표에서 Q(t)에 들어갈 내용으로 옳은 것은?

| φ | S | R | Q(t) |

|---|---|---|------|

| 1 | 0 | 0 | (a)  |

| 1 | 1 | 0 | (b)  |

| 1 | 0 | 1 | (c)  |

| 0 | X | X | (d)  |

| <u>(a)</u>        | <u>(b)</u> | <u>(c)</u> | <u>(d)</u> |

|-------------------|------------|------------|------------|

| ① 0               | 1          | 0          | Q(t-1)     |

|                   | 1          | 0          | Q(t-1)     |

| $\bigcirc Q(t-1)$ | 0          | 1          | 0          |

| $\bigcirc Q(t-1)$ | 0          | 1          | Q(t-1)     |

문 17. 다음 증폭기 회로에서 소신호 전압이득  $A_v = rac{V_o}{V}$ 의 표현식으로 적합한 것은? (단,  $g_m$ 은  $M_1$ 의 전달컨덕턴스이며, 채널길이변조 (channel length modulation)와 몸체효과(body effect)는 무시한다)

$$\textcircled{4} \quad A_v = \frac{g_m R_D}{1 + g_m (R_D + R_X)}$$

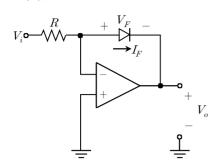

문 18. 이상적인 연산증폭기와 순방향 전류  $I_F = I_R \cdot e^{qV_F/kT}$ [A]의 특성을 갖는 다이오드를 이용한 다음 회로에서 출력전압 $V_o$ [V]는? (단,  $I_R$ 은 역방향 누설전류, q는 전자의 전하, k는 볼츠만 상수, T는 캘빈온도이다)

$$\label{eq:Vo} \ \, 3 \quad V_o = - \left( \frac{q}{kT} \right) \! \ln \! \left( \frac{V_i}{I_R \! R} \right)$$

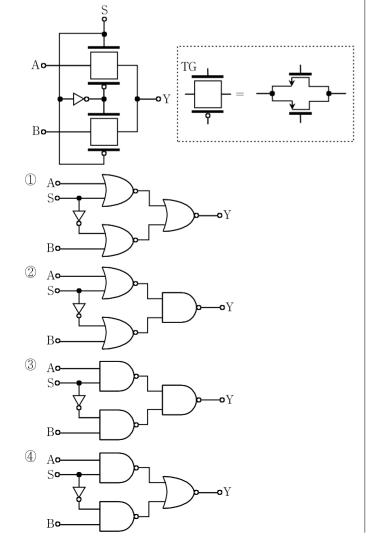

문 19. 다음 회로와 동일한 기능을 수행하는 논리회로는? (단, TG 게이트는 NMOS와 PMOS를 병렬로 연결한 것이다)

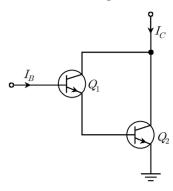

문 20. 전류증폭률이 각각  $h_{fe1}$ ,  $h_{fe2}$ 인 두 개의 트랜지스터  $Q_1$ ,  $Q_2$ 가 다음 회로와 같이 구성되었을 때,  $I_C[\mathbf{A}]$ 의 표현으로 옳은 것은?

- $\textcircled{1} \quad I_C = h_{fe1} \cdot h_{fe2} \cdot I_B$

- ②  $I_C = (h_{fe1} + h_{fe2}) \cdot I_B$